SPEAD Antenna Buffer Test

Purpose

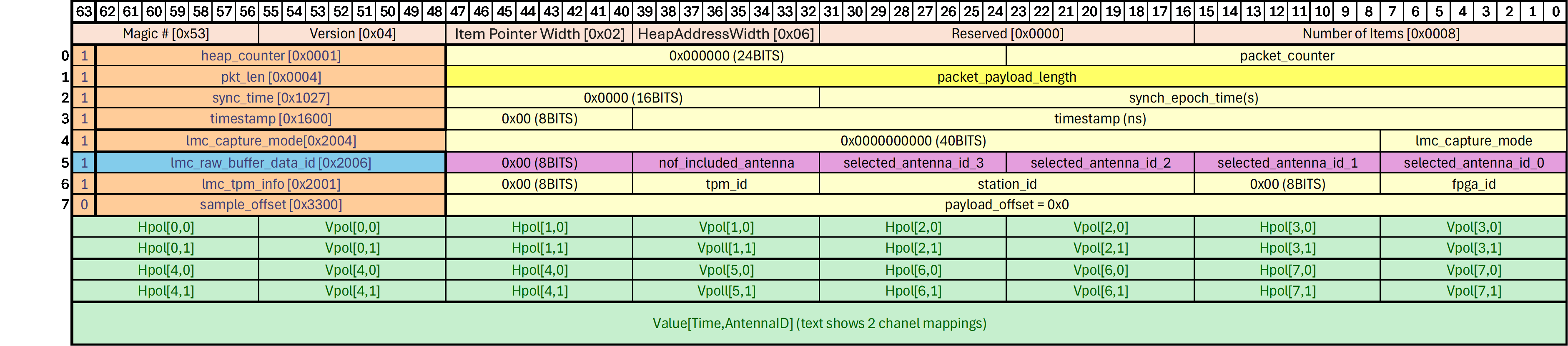

This test verifies the SPEAD header fields of the Antenna Buffer. The SPEAD packets are captured using the DAQ receiver. This test uses the SPEAD header metadata passed by the DAQ for verification. Given below is the SPEAD header specification which is verified in this test.

Antenna Buffer data is requested at 1 timestamp intervals. This corresponds to 864*512 samples of ADC data. Due to data being requested from each FPGA separately the test is run on one FPGA at a time.

Methodology

Establish connection to the station and specified TPM(s).

Sets up the Antenna Buffer, with the correct configration

Configure and initialise the DAQ receiver with the required UDP port and network interface.

Start the DAQ in Antenna Buffer data mode.

Request Antenna Buffer data for a specific TPM and FPGA, choosing 1 or 2 randomly selected antennas.

Wait for the DAQ to receive data.

Extract the spead header fields from the data callback.

Verify SPEAD header fields by comparing with the expected values.

Repeat steps 4-8 for set number of iterations

DAQ is then stopped, as the DAQ can only deal with a set number of tiles and antennas

Repeat steps 4-10 for all tiles and FPGAs

Stop the DAQ and clean up temporary directory.